Overview

The Magnetic Random Access Memories (MRAM) group develops advanced concepts in this emerging technology. The goal is to realize cells with improved thermal stability, lower power consumption and/or faster switching. Our research covers material stack deposition, nano-fabrication and electrical test evaluation, for applications as standalone memory and non-volatile logic and more recently in neuromorphic computing architectures.

Research directions

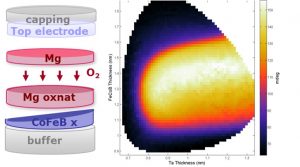

Perpendicular Anisotropy Materials

High energy barriers for spin transfer torque (STT) MRAM cells can be achieved with perpendicular anisotropy magnetic tunnel junctions. Solutions for high density MRAM cells to diameters below 20nm require continuous improvements in perpendicular surface anisotropy, while maintaining high TMR properties.

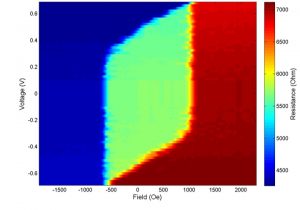

Perpendicular STT MRAM

Evaluation of MRAM concepts requires simulation of expected reversal mechanisms and electrical characterization of individual cells. We aim at understanding dynamics of magnetization reversal and the expected impact of stack modifications to explore application specific optimizations.

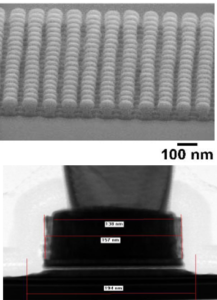

Nanofabrication Challenges

Innovation on dense MRAM using pre-patterned substrates, CMOS integration of multifunctional cells and sub-10nm lateral sizes. Tunnel junction nanofabrication in our platform is essential to evaluate MRAM concepts and performance.

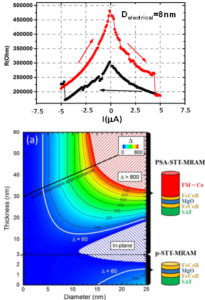

Perpendicular Shape Anisotropy

A solution for sub-10nm cell sizes uses high aspect ratios to generate perpendicular shape anisotropy providing scalable retention at the smallest cell sizes. Spin transfer torque switching is possible in these cells, where the reversal dynamics is now under study.

The team

Former members

Post-docs

- Andrey TIMOPHEEV (2014-2017)

- Van Dai NGUYEN (2016-2018)

- J. Ranier Roiz (2015-2016)

- Nikita Strelkov (2016-2019)

PhD

- Luc TILLIE (2015-2018)

- Nicolas PERRISSIN (2015-2018)

- Jyotirmoy CHATTERGEE (2014-2017)

- Hieu Tan NGUYEN (2013-2016)

- Antoine Chavent (2013-2015)

Process Engineers

- Jude GUELFFUCCI (2015-2017)

- Nathalie LAMARD (2016-2017)

- Guillaume LAVAITTE (2015-2016)

Projects

- Samsung SGMI (2014-2017)

- ANR Excalyb (2014-2017)

- Heumem (2015-2018)

- EU-FET Spice (2016-2019)

- EU Great (2016-2019)

- ERC Magical (2015-2020)

Partners

- CEA LETI, Grenoble, France

- Institut NEEL, Grenoble, France

- Crocus Technology, Grenoble, France

- Samsung, San Jose, USA

- Singulus AG, Kahl am Main, Germany

- Aarhus University, Aarhus, Denmark

- Radboud Universiteit, Neijmegen, Netherlands

Recent news

- GREAT – A H2020 ICT project at SPINTEC (June 30th, 2016)

Overview GREAT (European H2020 project) was accepted at the Summer 2015. Its kick-off meeting took place at SPINTEC in Grenoble on February 22nd-23rd 2016. The project aims at developing magnetic stacks able to equally perform memory, radio-frequency ... - SPICE – An H2020 FET project at SPINTEC (May 19th, 2016)

A new research project has been accepted at the last FET H2020 call. The objective of SPICE is to realize a novel integration platform that combines photonic, magnetic and electronic components. Its validity will be shown ... - Soutenance de thèse – Antoine CHAVENT (January 15th, 2016)

Jeudi 21 Janvier 2016 à 14H00, Phelma MINATEC – Amphithéâtre M001 (3 Parvis Louis Néel – 38016 Grenoble) Monsieur Antoine CHAVENT du DSM/INAC/SPINTEC soutiendra une thèse intitulée « Réduction du champ d’écriture de mémoires magnétiques à écriture assistée thermiquement ... - Improving writing properties of TAS-MRAM by changing the voltage pulse shape (January 11th, 2016)

During writing of Thermally Assisted Switching Magnetic Random Access Memory (TAS-MRAM), the torque due to a voltage pulse may be used to help writing. As part of collaboration between Spintec and Crocus Technology, we brought ... - Une mémoire STT MRAM sub-nanoseconde made in Spintec (December 09th, 2015)

Spintec développe une mémoire STT-MRAM dix fois plus rapide que les produits annoncés pour 2016 chez Samsung ou Intel. Sa vitesse d’écriture est inférieure à la nanoseconde, contre 5 à 10 nanosecondes habituellement. La différence ...