Overview

The transversal team aims at bringing together all competencies from SPINTEC involving spintronic devices nanofabrication, characterization, circuit integration, architecture, and algorithm techniques to implement hardware solutions for artificial intelligence (AI) and unconventional computing.

Spintronic-based multifunctional devices are a substantial opportunity to improve the energy efficiency of next-generation computing hardware. Moreover, this approach allows taking advantage of brain-inspired computing models to deploy cutting-edge neuromorphic algorithms, crossing the gap between current hardware AI implementations and exceptional brain computing ability.

Research topics

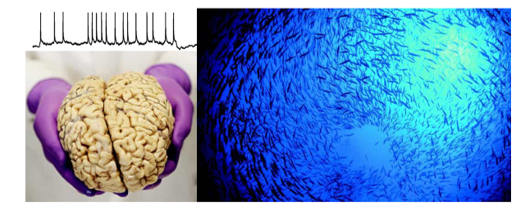

Bio-inspired computing

As the brain performs very sophisticated operations and consumes only a few Watts, brain-inspired/neuromorphic computing is a promising path for which spintronic devices can efficiently emulate both neurons and synapses in hardware. Their nanometric size, sensitivity to input stimuli, and interactions make those devices ideal for implementing large arrays of neuro-synaptic elements: spintronic nano-oscillators, spintronic and ferroelectric memristors, magnetic memories, superparamagnetic tunnel junctions, skyrmions, etc.

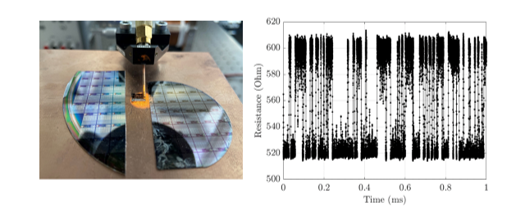

Probabilistic computing

Noise is a crucial ingredient in emulating the stochastic nature of the neural activity and executing energy-efficient computing algorithms such as energy-based or temporal-based machine learning models. In this context, probabilistic computing is a very suitable approach that relaxes usual precision computing constraints. The truly random nature of spintronic devices (such as superparamagnetic tunnel junctions) makes them attractive for hardware implementations of probabilistic computing approaches.

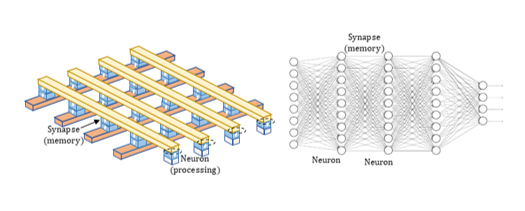

In memory computing

The most promising solutions for non-Von Neumann, in-memory computing architectures are based on the use of emerging technologies, that are able to act as both storage and information processing units thanks to their specific physical properties. High accuracy, Deep neural networks (DNN) can be built with crossbars analog in memory computing concept, involving MRAM families, such as STT, SOT, VCMA, but also with more exotic families of magneto-resistive, and ferroelectric or skyrmion based devices.

The team

Projects

Partners

- CEA LIST

- UMPHY

- CEA LETI

Recent news

- PhD Defense – MRAM based neuromorphic cell for Artificial Intelligence (January 26th, 2024)

On Friday February 16th, at 14:00 Louis Farcis (SPINTEC) will defend in English his PhD thesis entitled : MRAM based neuromorphic cell for Artificial Intelligence Place : IRIG/SPINTEC, CEA Building 10.05, auditorium 445 (access needs authorization request ... - Resistively-coupled stochastic MTJ for energy-based optimum search (January 22nd, 2024)

We study recurrent networks of binary stochastic Magnetic Tunnel Junctions (sMTJ), aiming at efficiently solving computationally hard optimization problems. After validating a prototyping route, we investigate the impact of hybrid CMOS+MTJ building block variants on ... - SpinDrop: Dropout Based Bayesian Binary Neural Networks with STT-MRAM (October 16th, 2023)

Bayesian NN (BayNN) using Dropout-based approximation provides a systematic approach for estimating the uncertainty of predictions. Despite such merit, they are not suitable for implementation in an embedded device and in most cases cannot meet ... - PhD offer – Reliable In Memory Computing Implementation of stochastic ultra-low-power bioinspired neural networks (October 10th, 2023)

Context The automated resolution of cognitive tasks primarily relies on learning algorithms applied to neural networks which, when executed on standard CMOS based digital architectures, lead to a power consumption several orders of magnitude larger than what the ... - PhD Defense – Models and algorithms for implementing energy-efficient spiking neural networks on neuromorphic hardware at the edge (August 31st, 2023)

On Monday September 04th, at 14:00, Manon DAMPFHOFFER (SPINTEC) will defend her PhD thesis entitled : Models and algorithms for implementing energy-efficient spiking neural networks on neuromorphic hardware at the edge Place : GreEn-ER – Grenoble INP- ...