Radiation robust circuit design for harsh environments like space is a big challenge for IC design and embedded systems. As circuits become more and more complex and CMOS processes get denser and smaller, their immunity towards particle strikes decreases drastically. Spintec proposed a novel integrated circuit structure that enable to increase to increase the robustness in space environment.

For critical applications (aviation and/or space), it would be desirable to provide a circuit that is rendered robust against the effects of radiation. Indeed, the presence of ionizing particles at high altitudes or in space can induce currents in integrated circuits that may be large enough to cause a flip in the binary state held by one or more gates. This may cause the circuit to malfunction, known as a single event upset (SEU). Furthermore, if SEUs occur at a relatively high rate, it may even be impossible for a processing operation to be completed before a reset is required. There is thus a need in the art for a circuit having relatively low surface area and power consumption, and that allows recovery following an SEU without requiring a reset.

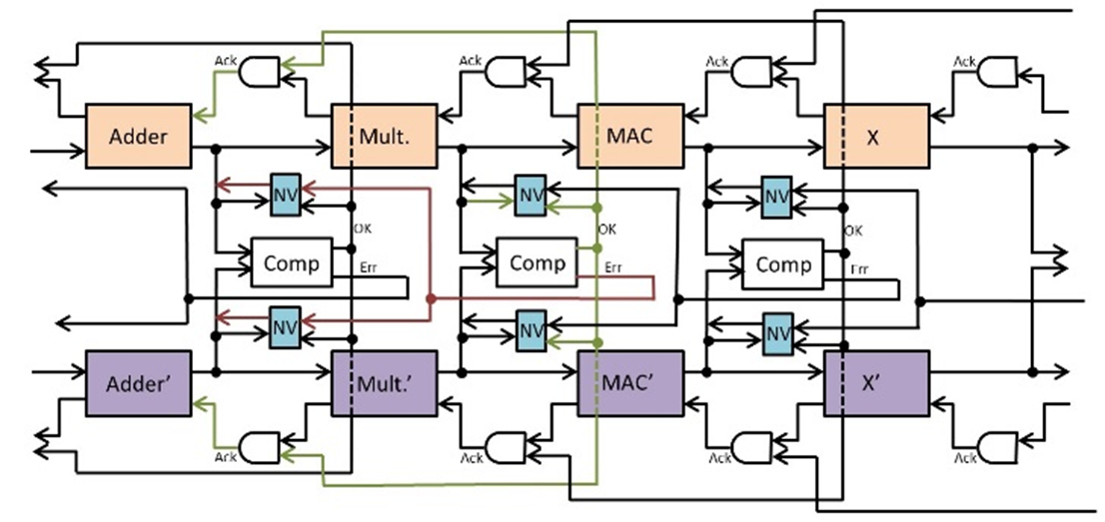

The figure shows an error correcting asynchronous, or clock-less, structure. This structure is composed of a pipeline that comprises a series of asynchronous stages, such as an adder, a multiplier, a multiplier/accumulator and/or any asynchronous function. This pipeline is duplicated, the second series of stages (differentiated by an ’) being also the same operators. The second series of stages are functionally equivalent to the first and will generate identical output signals in the absence of error. There is a comparator coupled to the output data lines of each of the stages. Each comparator generates an error signal when a mismatch is detected between the data signals from corresponding pipeline stages. This error signal controls a mechanism that is inserted in the return acknowledgement signal of each stage. This mechanism, based on the error signal resulting from the comparison of the data signals from two stages, can activate or pause the propagation of the acknowledgement signal to the previous stage. If a mismatch occurs, the error signal from the comparator of that stage will block the acknowledgement signals going to the previous stage. By doing this, the previous stage continues to provide the same output and the stage concerned by the error can re perform its calculation, thus correcting the error. This is made possible by the delay insensitive properties of asynchronous communication protocol. The circuit can locally be paused waiting the dissipation of an error without affecting the global functionality of the system.

MRAM-based asynchronous pipeline structure robust again particle strikes

This structure also integrates MRAM-based non-volatile storage circuits represented by NV. Each Magnetic Tunnel Junction (MTJ) storage circuit is configured to store the data signals at the output of the corresponding pipeline stage if the comparator of the stage does not indicate any error. However, if an error is detected by the comparator of a stage, the MTJ non-volatile storage circuit of the previous stage is adapted to output its stored value, which will overwrite the wrong value provided by that stage. This way the circuit is immune to any further SEU occurring in any stage. Finally, the MTJ non-volatile storage circuits permit the pipelines to be re initialized from a stored state following a reset or power down of the pipeline. This can be a further improvement in terms of power consumption. Such an ASIC using MRAM-based asynchronous design architectures enables to improve radiation robustness without really increasing the circuit area compared to the state of the art.

We would like to thank the CEA and CNES for their financial support for this Ph.D., as well as the LIRMM, LETI and CNRS for their implication.

Gregory.DiPendina@cea.fr