Internet of Things (IoT) applications deployment relies on low-power and security constraints. In this perspective, lightweight cryptography has been developed.

This field enables, with a reduced area and power consumption, to encrypt sensitive data processed in an integrated circuit and transmitted to a connected object.

This work proposes to implement the PRESENT lightweight cryptographic algorithm using STT-MRAM in order to improve its performance compared to a pure CMOS cipher.

The number of communicating data exploded with the IoT deployment.

However, with time-to-market pressing demand, the security of this data is not always guaranteed.

In this context, this work proposes to design a hybrid CMOS/STT-MRAM PRESENT cryptographic algorithm in different technology nodes in order to reach a better power efficiency compared to a CMOS cryptographic algorithm, enabling then its integration in the IoT.

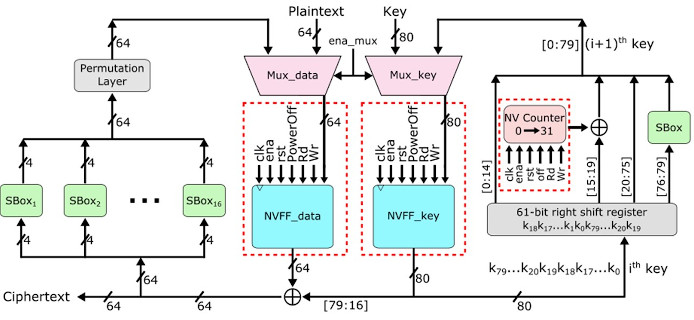

Proposed hybrid CMOS/STT-MRAM PRESENT cryptographic algorithm.

a) Evaluation of the area in GE (Gate Equivalent) and the overhead evolution compared to the pure CMOS structure. b) Sleep energy evolution (nJ).

The first implementation of this structure was realized using a 180 nm bulk CMOS process and 200 nm STT-MRAM junction diameter (scenario #1 in the figure).

Electrical simulations of this hybrid algorithm has demonstrated a better power efficiency of this architecture for “normally-off” applications.

Actually, the hybrid CMOS/STT-MRAM algorithm of scenario #1 is power efficient after 675 ms of inactivity compared to the CMOS version, which is already interesting for many IoT applications. Indeed, unlike the CMOS that has standby power consumption, the hybrid version does not consume energy while it is off. However, its physical implementation is 9 times larger than the pure CMOS one. Several evaluations were realized for different technology nodes down to the 28 nm FD-SOI and a junction size diameter of 40 nm (scenario #2). In this case, the area overhead is limited to only 23 % and the power efficiency is reached after only 185 µs. Therefore, such a configuration is really interesting for energy saving in many applications not limited to IoT.

In perspective, the circuits that have been fabricated (CMOS and scenario #1) as part of the GREAT project will be shortly tested in order to determine their response facing physical attacks, aiming to retrieve the secret data.

Team: Spintronics IC design

Collaboration: CEA tech (Gardanne), IM2NP – Aix Marseille University (Marseille).

Funding: GREAT European project, MASTA ANR project.

Further reading: Light-Weight Cipher Based on Hybrid CMOS/STT-MRAM : Power/Area Analysis, M. Kharbouche-Harrari, G. Di Pendina, R. Wacquez, B. Dieny, D. Aboulkassimi, J. Postel-Pellerin and J-M. Portal, In 2019 IEEE International Symposium on Circuits and Systems (ISCAS). DOI: https://doi.org/10.1109/ISCAS.2019.8702734

Contacts:gregory.dipendina@cea.fr, mounia.kharbouche@cea.fr