Two-dimensional (2D) materials like transition metal dichalcogenides (TMD) are considered as key candidates to replace silicon in several technologies with enhanced performances. In this work, we address the two remaining challenges to reach their industrial deployment: the wafer scale growth of TMDs and their integration into operational devices using CMOS compatible process. This is achieved with MoS2-based memristors in which we conclude that electrical switching takes place in grain boundaries.

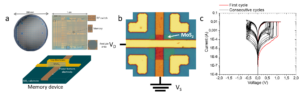

(a) Wafer-scale planarized electrodes on which large area MoS2 is transferred and schematics of the MoS2-based memristor. (b) Optical image of the memristor showing bottom, top electrodes and the MoS2 patch (in green). (c) Electrical measurements: ON (low resistivity) and OFF states (high resistivity state) are clearly observed.

2D materials like TMDs are promising materials to develop high-performance electronic devices. In particular, MoS2 was used in flexible devices, sensors, high responsivity phototransistors, non-volatile memory devices, high cut-off frequency RF switches or transistors. For memory devices, MoS2 has been integrated in nanoscale vertical metal-insulator-metal (MIM) structure with low switching voltage, fast switching speed and high ON/OFF current ratio enabling the manufacture of multi-level devices, opening the way to the development of RF switches and neuromorphic devices. However, large-scale integration of such devices has not yet been demonstrated and the exact atomic mechanisms for the formation of ON and OFF states not yet understood in particular because of the low yield of switching devices, lack of reproducibility and weak endurance after manufacturing.

In this study, we have developed and optimized a complete process for integrating 2D materials into a fully CMOS-compatible vertical MIM structure in a clean room and over large area (see figures (a) and (b)). We demonstrated the preservation of the physico-chemical properties of MoS2 during the whole fabrication process and the high-quality of van der Waals interfaces. Electrical measurements (see figure (c)) were performed to understand the influence of the fabrication protocol, the top electrode metal and the MoS2 grain size on devices performances.

Thanks to the process optimization, the yield of switching devices, reproducibility and performances were greatly improved. More specifically, ON/OFF current ratios up to 105 were obtained, which is promising for the manufacture of RF switches. By reducing the stochastic behavior of the devices, we could reliably investigate the switching mechanism. Statistics on the switching voltage and distribution of MoS2 devices with two different grain sizes demonstrated that grain boundaries are the preferred location for the formation of conduction filaments. We concluded that the quality of MoS2 layers, in particular the grain size, is a key factor to adjust the performances of MoS2-based memories.

Team: 2D SPINTRONICS

Collaboration: CEA LETI, PFNC, PTA

Funding: PEPR Microelectronics ADICT

Further reading: Development and optimization of large-scale integration of 2D material in memristors, C. Ligaud, L. Le Van-Jodin, B. Reig, P. Trousset, P. Brunet, M. Bertucchi, C. Hellion, N. Gauthier, L. Van-Hoan, H. Okuno, D. Dosenovic, S. Cadot, R. Gassilloud and M. Jamet, 2D Mater. 11, 045002 (2024). Open access: hal-cea-04724987v1

Contact at Spintec: Matthieu JAMET