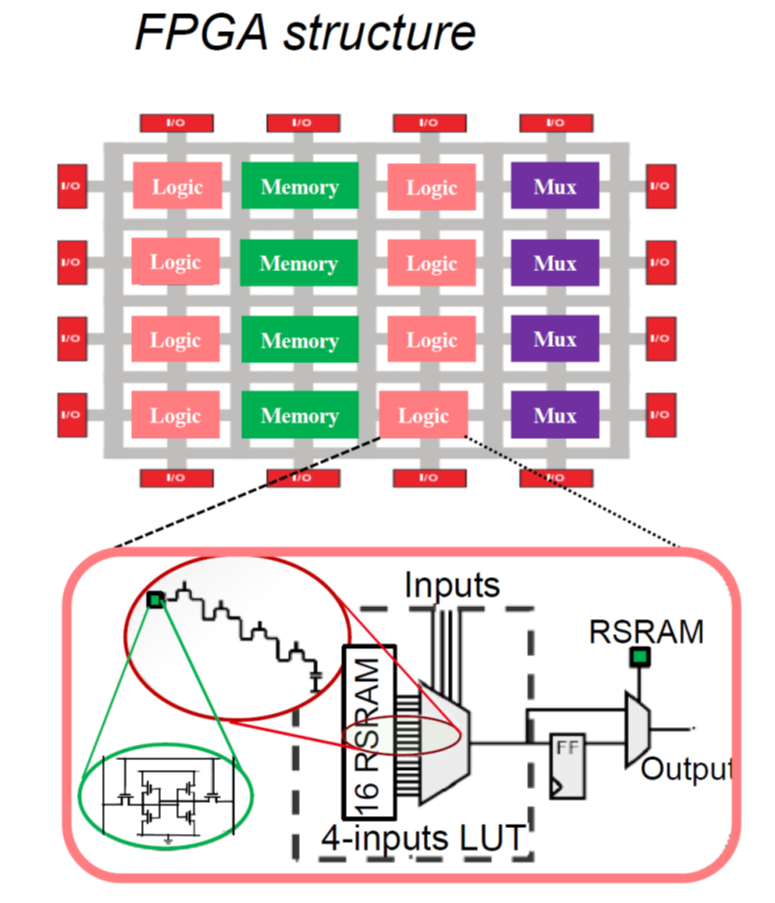

In the framework of an internal collaborative project between CEA-LETI and CEA/CNRS/UGA-SPINTEC Lab, Rana Alhalabi proposed a new Look Up Table (LUT) architecture, which is one of the elementary cell of FPGAs (Field Programmable Grid Array). This innovation offers a 55% sense delay reduction, 47% number of MTJ reduction, 46% power-delay product reduction and a wider input number increase. She has been awarded of the best poster award during the Ph. D. student day of the Electronics Electrotechnics Automatism and Signal Processing doctoral school (EEATS) of Grenoble University (UGA).