Due to its good radiation effects tolerance and its inherent non volatility, Spin-Transfer Torque Magnetic Tunnel Junction (STT-MTJ) is considered as a promising candidate for high-reliability electronics. A radiation tolerant circuit design suitable for space application is proposed in this study.

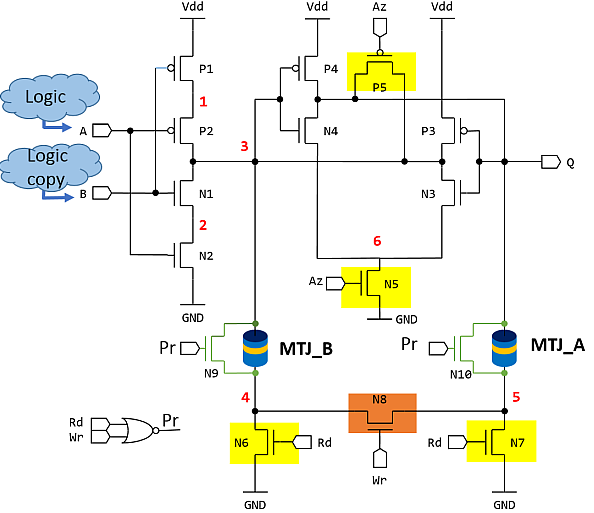

Proposed radiation-tolerant sequential circuit. The numbers in the circuit represent the nodes most sensitive to radiation.

Radiation effects research on semiconductors has been pursued since the 1960s becoming an extremely vivid area of research and development. Nevertheless, for embedded systems in space environments, a radiation robust circuit design is still an open challenge.

The Spintronics Integrated Circuit Design team of Spintec investigated Radiation Hardening by Design Techniques combined with FD-SOI 28 nm process, attested to be six times more resilient than bulk technology to heavy-ion irradiation, with non-charge based memory: the Spin Transfer Torque Magnetic Tunnel Junction. The proposed logic-in memory circuit is a sequential block able to mitigate the impact of Single Event Effect due to heavy ions strikes. MTJs are used to store the output state and its complement, while the CMOS part takes charge of the combinational operations. In this context, the main problem still to be faced is the unwanted switching of magnetic devices due to the activation of surrounding peripheral circuits as a particle strike consequence.

Two different strategies have been pursued in order to ensure robustness of the MTJ state against particle strikes. First, the impact of the different MTJ parameters on switching was evaluated by calibrating parameters within the compact model used in the electrical simulation environment. Next, reduction of the current flowing though the MTJs induced by a strike was achieved by inserting a transistor in parallel to each MTJ. The key idea is to obtain a less resistive shunt path for the current pulse induced by particle strikes. Experimental test campaigns are planned in the next future. If the robustness to high radiation rate is confirmed, a suitable strategy for space circuit design could be to replace as many transistors as possible with magnetic devices, using the logic-in-memory concepts based on purely magnetic logic gate.

Teams: Spintronics Integrated Circuit Design

Collaboration: LIRMM (Montpellier); CNES (Toulouse)

Funding: CNRS-CNES

Further reading: Spin-Transfer Torque Magnetic Tunnel Junction for Single-Event Effects mitigation in IC Design, O. Coi, G. Di Pendina,, G. Prenat, L. Torres, IEEE Transactions on Nuclear Science 67, 1674 (2020).

Contact: Gregory DI PENDINA